把半导体制造技术留在日本——日本的国家项目“先端半导体制造技术开发”带着这个悲壮感的目标于2021年度启动。半导体代工巨头台湾积体电路制造(TSMC)的参与也引发了关注。

位于茨城县筑波市的“产业技术综合研究所”的设施将作为项目基地(供图:产综研)

该项目是新能源产业技术综合开发机构(NEDO)2019年度开始推进的项目的一部分。以拥有最先进清洁车间的产业技术综合研究所(茨城县筑波市)为基础,企业和大学将在这里开发具有支撑数字社会发展的运算功能的逻辑半导体制造技术。

| 项目概要 | |

| 名称 | 先端半导体制造技术开发 |

| 内容 | 开发“后5G”时代的尖端逻辑半导体制造技术,确保可以在国内制造 |

| 开始 | 2021年度 |

| 预算 | 760亿日元(5年的预估补助额) |

| 参与机构 | 产业技术综合研究所、东电电子、佳能、TSMC日本3DIC研究开发中心、先端系统技术研究组合等 |

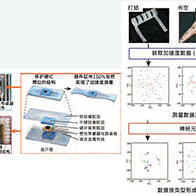

半导体制造工序分为利用曝光设备等在硅基板上形成电路的“前工序”和将其切割并组装的“后工序”。本次的项目也以这两道工序为研发主题,共同的关键字是“三维”。

前工序致力于将名为“纳米片”的微细结构上下排列的最尖端器件技术。目前逻辑半导体的基本结构已经由在基板表面形成的二维“平面型”变成了切削基板制作有一定厚度的“鳍型”,其被称为“2.5维”。预计2025年以后三维纳米片型将成为主流。

日本拥有量产技术的是平面型,该项目将跳过鳍型,直接致力于三维纳米片型。东电电子、迪恩士(SCREEN Semiconductor Solutions)和佳能将在产综研的设施里建设试产线。

后工序将确立纵向堆叠的积层电路技术。主角为TSMC的日本研究基地TSMC日本3DIC研发中心。计划与日本方面共同开发名为“3DIC”的三维后工序技术。作为其他开发项目,产学共同参与的“先端系统技术研究组合(RaaS)”将致力于芯片的三维积层技术。

三维集成是打破半导体微细化“摩尔定律”极限的有力技术。尤其是后工序相关的技术,日本企业被认为拥有优势,受此吸引的TSMC与希望联合该公司的日方想法刚好一致。

文:吉川和辉 编辑委员、《日本经济新闻》,2022/04/04

翻译编辑:JST客观日本编辑部