本文根据产综研成果发布编译整理而成

以日本国立研究开发法人产业技术综合研究所(以下简称“产综研”)器件技术研究部门尖端CMOS技术研究团队的张文馨研究员为代表的日本团队(产综研和东北大学),与以国家实验研究院台湾半导体研究中心的李耀仁研究员为代表的台湾团队(国立交通大学、国立成功大学、国立暨南国际大学、国立台湾大学、国立中山大学、逢甲大学、工业技术研究院、日立先端科技台湾公司)经过联合研究,面向2nm工艺开发出了Si和Ge的异质沟道互补式场效应晶体管hCFET(heterogeneous Complementary-Field Effect Transistor)。

相关技术详情将在2020年12月12~16日在线举行的2020 IEEE International Electron Devices Meeting(IEDM 2020)上发表。

研究团队此次开发了上下层叠Si和Ge的沟道薄膜的技术,实现了以最短距离连接Si n型FET和Ge p型FET的hCFET构造。通过缩小集成电路的三维结构,有望大幅提高集成度及进一步提高速度。

Si/Ge异质沟道互补式场效应晶体管hCFET

开发背景

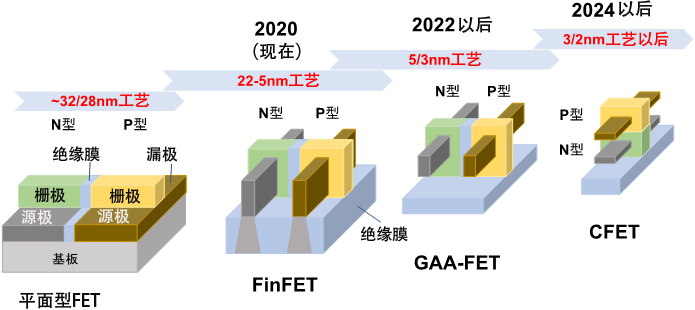

随着移动信息终端和IT设备等的爆发性普及,电子信息设备需要提高性能和削减耗电量。图1是负责信息处理的场效应晶体管(FET)发展蓝图。通过推进FET的微细化,平面型CMOS结构遵循摩尔定律实现了高性能和低功耗,但二维结构的微细化达到了物理极限,从22nm工艺前后开始发生重大变化,转向了三维FET结构。Fin FET是拥有鳍(Fin)状栅极结构的FET,目前已实用化。由其发展而来的是栅极完全覆盖了沟道的上下左右部位的GAA(Gate All Around)结构。今后进一步进化的FET结构将是上下层叠n型FET和p型FET的CFET结构。这种结构能以原来的单个FET元件的尺寸构成CMOS,可以大幅削减面积和提高速度。

另一方面,Si以外的沟道材料的研究开发也在进行中。与Si相比,Ge的空穴迁移率比较高,能以低电压工作,与Si工艺的亲和性也比较高,因此n型FET利用原来的Si、p型FET利用Ge制作的异质沟道集成平台作为FET的高速化技术备受期待。

图1:FET发展蓝图

研究内容

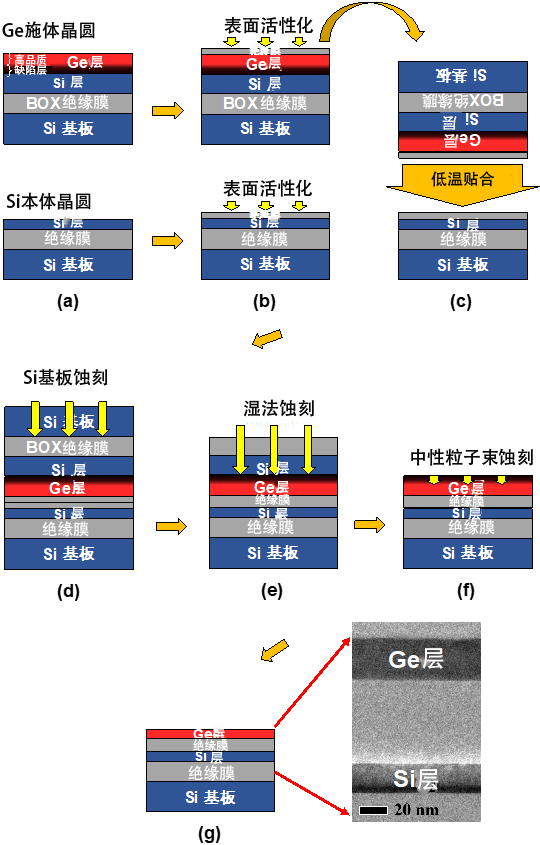

产综研和TSRI构筑了层叠Si层和Ge层的Si/Ge异质沟道集成平台。层叠Si和Ge等热膨胀率不同的材料时,为避免热应力的影响,需要在尽量低的温度下进行层叠。研究团队开发出了在低于200℃的温度下层叠高品质Si层和Ge层的低温异质层键合技术(Low Temperature Hetero-layer Bonding Technology, LT-HBT,图2)。

图2:采用低温异质层键合技术的Si/Ge异质沟道积层工艺

此次开发的技术首先准备了SOI主体晶圆(Host Wafer)和在上面外延生长Ge的施体晶圆(Donor Wafer,a)。在Ge层中,与Si层的界面附近的位置存在缺陷层,表面侧存在高品质层。接下来,分别在施体晶圆和主体晶圆上沉积SiO2绝缘膜,激活表面后(b),以200度的低温直接键合(c)。然后依次去除施体晶圆的Si基板(d)、BOX绝缘膜和Si层(e)。最后,利用东北大学开发的可低损伤加工的中性粒子束蚀刻法(Neutral Beam Etching, NBE)将Ge均匀成膜(f),即可获得Si/Ge异质沟道积层结构(g)。通过使积层工艺和蚀刻工艺全部在低温下进行,实现了对Si层和Ge层的损伤非常小的高品质Si/Ge异质沟道集成平台。另外,利用该技术,不仅可以大幅简化hCFET制作工艺,还支持进一步增加层数的结构。

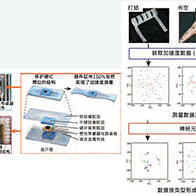

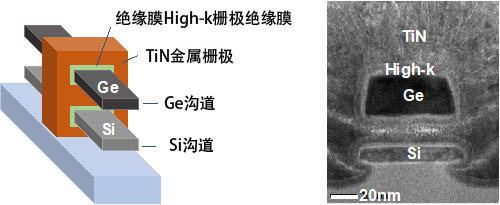

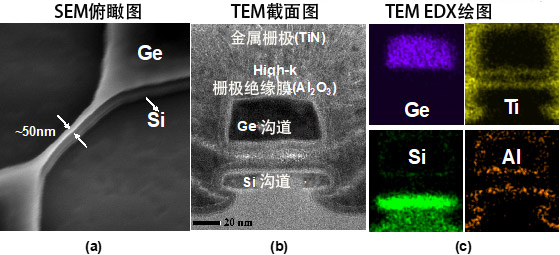

研究团队利用该Si/Ge异质沟道积层平台制作了hCFET(图3)。通过以相同的沟道图案形成Si和Ge层,并对Si层与Ge层之间的绝缘层进行蚀刻,得到了纳米片状积层型沟道结构。从图3(a)的SEM俯瞰图可以看出,Ge和Si沟道是裸露的。通过以覆盖整个沟道的形式在该结构上沉积high-k栅极绝缘膜/金属栅极,实现了上下层叠Si n型FET和Ge p型FET的GAA结构hCFET(图3(b))。可以看到以沟道宽度约为50nm的纳米片状在上部层叠Ge层,下部层叠Si层的结构。TEM EDX分析显示,Si/Ge异质材料沟道被high-k栅极绝缘膜(Al2O3)和金属栅极(TiN)覆盖(图3(c))。另外,还通过单一的栅极成功地使这些n型FET和p型FET同时作为晶体管工作,表明基于LT-HBT的异质沟道积层化作为2nm工艺的晶体管技术非常有效。

图3:上下层叠Si n型FET和Ge p型FET的三维异质沟道互补式场效应晶体管(hCFET)

日语发布资料

编译:JST客观日本编辑部