东京工业大学工学院电气电子系的冈田健一教授等人与日本电信电话公司组成的研究团队,成功开发出了采用300GHz频带的超高速无线通信收发器,频率达到5G使用的28GHz频带的10倍。

这款无线收发器的发送和接收功能加在一起,只需410mW的低功耗即可实现34Gbps(Gbit/秒)的高速无线通信。通过采用新设计的高增益混频器电路,可利用能低成本量产的硅CMOS工艺制造。

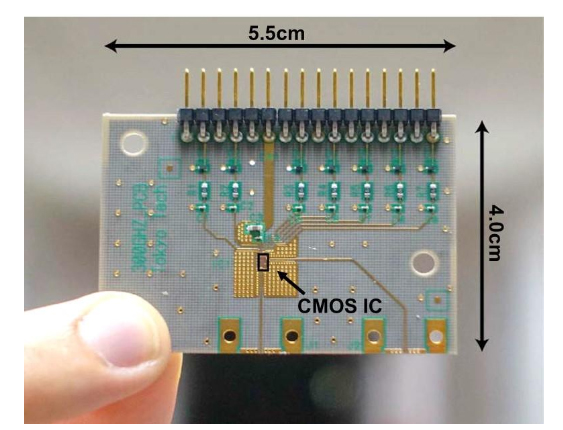

图1:新开发的300GHz频带无线设备IC(安装在印刷电路板上后)

随着实现低成本化、小面积化和节电化,可以将其配备于智能手机等移动终端。这一成果将加速推进5G的下一代无线通信系统的实用化。

相关论文已在8月4日开始在线举行的国际会议IMS 2020(International Microwave Symposium 2020)上发表,演讲题目为“A 300GHz Wireless Transceiver in 65nm CMOS for IEEE802.15.3d Using Push-Push Subharmonic Mixer“。

开发背景

日本从2020年3月开始提供5G服务,关于5G的下一代无线通信的研究也已经在积极推进。为实现更高速度、更大容量的无线通信,比5G的毫米波频带高10倍以上的300GHz频带的利用备受期待。

一般来说,5G利用28GHz频带的频率可实现最高10Gbps的通信速度。通过进一步提高频率,采用300GHz频带,有望增加可利用的通信带宽,实现最高300Gbps以上的无线通信。为尽快实现300GHz频带无线设备的实用化,亟需开发小型、低成本,而且将来可以配备于移动终端的节电技术。

课题

此前也发布过采用成本方面占优势的硅CMOS工艺的300GHz频带无线设备,但存在难以削减耗电量和电路面积的课题。原因是,300GHz频带难以在硅CMOS上实现放大器,在这样的制约下,要想提高无线设备的输出功率,就要采用多个小输出功率的电路,然后使输出功率相加。

因此,无线IC上配备的收发器的数量就会增加,导致耗电量和面积增大。另一方面,采用高频特性更优异的磷化铟(InP)等化合物半导体,也可以实现300GHz频带的放大器,但在集成方面存在课题。

研究成果

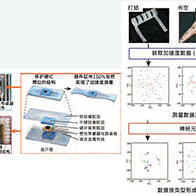

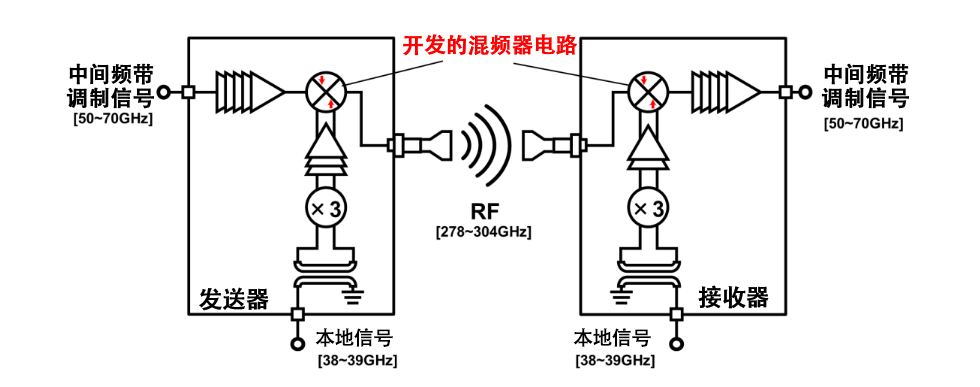

本研究新设计了高增益混频器电路,从而成功开发出即使采用硅CMOS工艺也能以小面积、低功耗工作的无线收发器。图2是此次开发的无线收发器的整体构造。发送器和接收器都采用新开发的混频器电路,因此无需在天线和混频器之间安装放大器,即可实现无线通信所需的高信噪比(SNR=Signal-Noise Ratio)。

图2:新开发的300GHz频带无线收发器的构造

在以往的混频器中,中间频带的调制信号和用于变频的本地信号都从同一个端子输入,因此利用晶体管的电压电流转换的非线性进行变频,难以提高混频器电路的增益(电路的输入输出比)。另外,还要使两种信号的阻抗匹配,因此需要使中间频率和本地信号频率在同一频带内,而且调制波信号和本地信号都需要使用超过100GHz的放大器。

放大器的耗电量会随着频率增加,这是以往的无线收发器耗电量较大的原因之一。此次新设计了可以使调制信号和本地信号从不同端子输入的混频器电路结构。通过采用这种结构,可以利用晶体管的开关进行变频,成功地将混频器电路的增益较原来提高了约2倍。另外,利用这种方式还可以将中间频率设定为100GHz以下,因此能大幅削减耗电量。

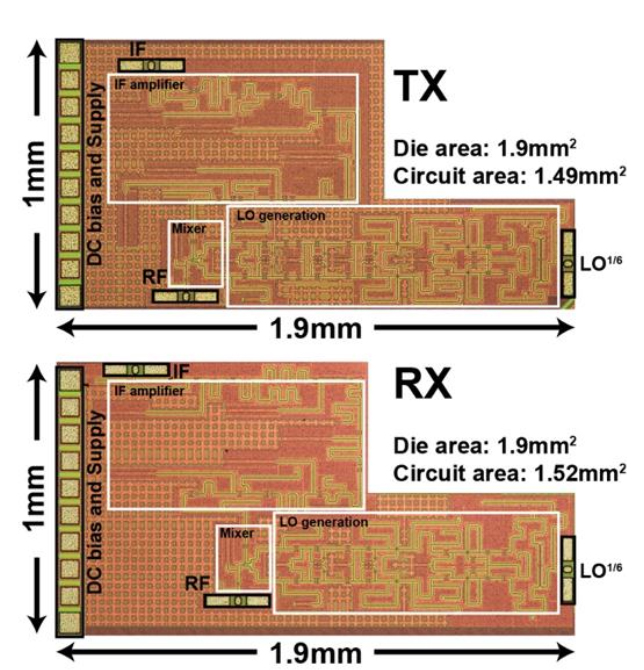

研究团队利用硅CMOS 65nm工艺试制了新开发的300GHz频带无线收发器(图3),通过对300GHz频带的无线通信特性进行测量评估,确认了所提出的技术的有效性。收发器可在278GHz至304GHz的频率下满足IEEE802.15.3d无线标准规定的频谱模板(Spectrum Mask),能应对从QPSK到16QAM的调制方式。

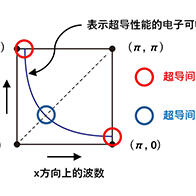

图3:试制的无线收发IC的照片

最大通信速度为34Gbps,此时,发送器和接收器的耗电量共410mW,与此前研究中采用硅CMOS工艺的300GHz频带收发器相比,耗电量降至四分之一以下。另外,无需使用多个收发器进行功率合成,只使用一个收发器即可构成,因此收发器整体的芯片面积只有3.8mm2,节省了面积。

未来展望

此次开发的300GHz频带无线收发器采用硅CMOS工艺,节约了耗电量和面积。从而可以削减无线设备的尺寸,配备于移动终端,通过CMOS工艺节约了面积的无线IC还有助于降低无线设备的成本。今后将以此次的研究成果为基础继续推进开发,计划进一步提高速度,使新一代100Gbps以上的超高速、大容量300GHz频带无线通信实现实用化。

文:JST客观日本编辑部