日本电信电话公司(NTT)、九州大学、东京大学针对量子计算机的运转进行动态纠错,在全球首次提出了可大幅削减被视为容错量子计算机发展障碍的突发错误影响的量子计算机架构。

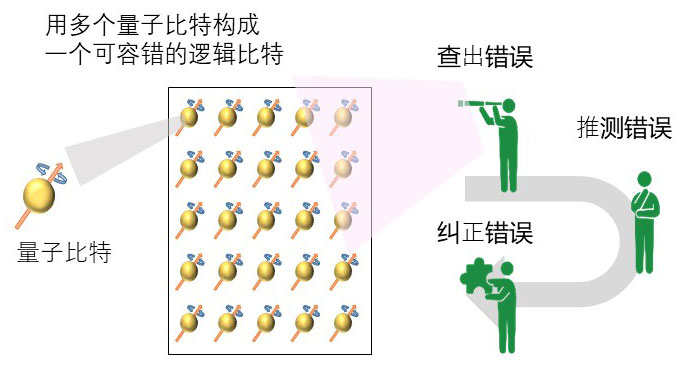

图1纠错示意图(图片由NTT提供)

量子比特只要持有的信息泄漏到外部就会出错,所以即便是不会导致普通计算机发生错误的环境噪声,对量子计算机来说也会成为导致产生错误的原因。

近年来,随着量子技术的发展,可控的量子比特数出现了增加,但随着集成化的发展,计算中的低概率错误特性的变化会对量子纠错的性能产生较大的影响。为此,还必须应对因宇宙射线产生的突发错误。

研究团队提出的架构,能够通过在控制量子计算机的普通计算机控制机构中追加逻辑单元,从而大幅降低超导量子比特因宇宙射线产生的突发错误的持续时间和影响范围。这种方法无论在何种部件上,适用于满足一定特性的任何突发错误。

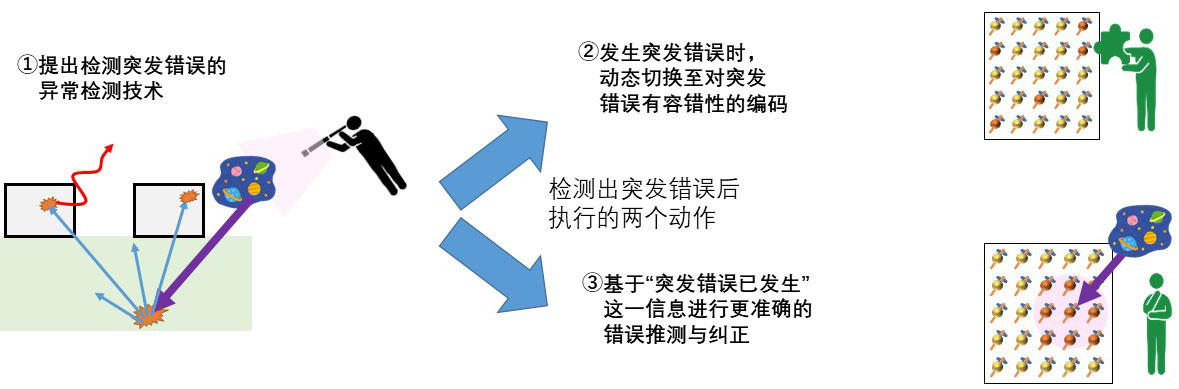

该架构的关键在于异常检测、动态编码方式的变形和错误推测的再执行。首先是通过异常检测技术,在短暂的延迟内检测出突发错误的发生。研究团队提出了一种检测技术,此时并不直接测量量子比特,而是从被用作错误推测提示的奇偶校验值的统计结果推测出突发错误的发生。

一旦通过异常检测发现突发错误的发生,就会执行两个用于减轻突发错误影响的动作。一是立即切换至效率虽低但对突发错误具有容错性的编码方式,此举能够在突发错误被检测出后将其影响几乎降至为零。这是一种以非严格对应进行中断处理的编码机制。与此同时,倒退回突发错误到来之前的状态,基于“突发错误已发生”这一信息进行更准确的错误推测,从而进一步减轻从突发错误的发生到被检测出来这段时间里产生的影响。

图2)提出的方法:突发错误的检测和应对(图片由NTT提供)

研究表明即使将这样的追加机制组装到控制装置中,也不会影响量子计算机本身的速度。

东京大学研究生院工学系研究科的小芦雅斗教授表示:“这可以说是实现大规模容错量子计算机的一个重要进展。”

原文:《科学新闻》

翻译:JST客观日本编辑部

【论文信息】

学会:在The 55th IEEE/ACM International Symposium on Microarchitecture(MICRO-55)

论文:Q3DE: A fault-tolerant quantum computer architecture for multi-bit burst errors by cosmic rays