NTT与名古屋大学和东京大学组成的研究团队合作开发出了可在驱动超导量子计算机的极低温环境下,满足控制具有实用性规模量子计算机所需的耗电量、安装规模、速度和纠错水平的量子纠错方法,这在世界上还是首次。此次的成果有望为目前各国竞相开发的容错量子计算机做出重要贡献。

三方今后打算将研究成果的设计具体安装到芯片上,通过实验来证明量子计算机可以进行量子纠错。另外,还打算以此次的成果设计为基础,使其支持由表面代码构成的逻辑量子比特运算机制,为此将解决扩展等课题。

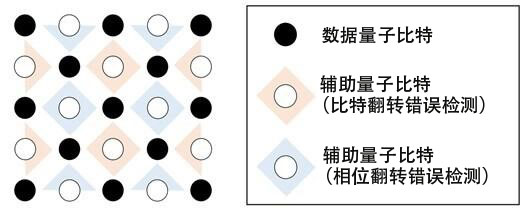

图1:表面代码(图片由NTT提供)

普通(经典)计算机的信息单元——“比特”的值为0或1,而量子计算机的信息单元——“量子比特”除了0和1外,还可以是0和1的连续叠加态。量子计算机的一个特性是,可以利用这种叠加态同时执行比特值为0和1的计算,但观测量子比特时,这个值便会确定为0或1,叠加态坍缩。

量子比特容易发生错误,量子计算机的计算需要纠错,但因为上述特性,无法通过直接观测量子比特来调查是否存在错误。因此,研究人员提出了对具有不同作用的多个物理量子比特进行编码,从而形成一个逻辑量子比特的框架——量子纠错码。

其代表之一就是表面代码。表面代码由有序排列的数据量子比特和用于观测的辅助量子比特构成。数据量子比特用于表示逻辑量子比特的叠加态,不直接观测。不过,辅助量子比特的观测值会提示相邻的数据量子比特发生的错误。根据这些提示确定数据量子比特实际发生的错误的类型和位置称为解码。

这种表面代码的解码处理被归结为图形匹配问题,将解决匹配问题的普通计算机(称为解码器)与量子比特组合起来就可以构建容错的量子计算机。

目前已经有了几种实现量子比特的方法,尤其是超导量子比特,由于集成潜力和设计自由度比较高,作为量子计算机信息单元的第一候选备受期待。这种超导量子比特存在必须在极低温环境下工作的限制,因此一般在冷冻机中工作。

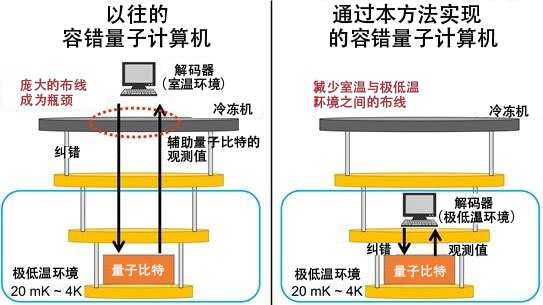

而量子纠错码的解码器一般在室温下工作,因此在不同的温度环境之间连接量子比特和解码器的庞大布线成为瓶颈,导致超导量子计算机的可扩展性受到限制。由于极低温环境下容许的耗电量非常小,所以在极低温环境下运行普通解码器是不现实的。

图2:超导容错量子计算机的构成,左边是以往的方法,右边是新提出的方法(图片由NTT提供)

所以,此次研究团队利用能以低功耗高速运行的单磁通量子(SFQ:Single Flux Quantum)电路,设计了可在极低温环境下工作的表面代码解码器。设计的解码器能以足够高的速度运行,可执行在量子比特发生错误后立即纠正以防止错误积累的在线解码。利用该方法能减少不同温度环境之间的布线,大幅提高量子计算机的可扩展性。另外,在线解码还能改善量子比特的容错性。

在此次的联合研究中,东京大学负责研究算法和芯片安装设计,以及与量子比特布线的可行性,NTT负责量子纠错的理论整理和解码器的性能评估,名古屋大学负责芯片安装和安装时的性能评估。

该研究思路中最重要的一点是,通过算法和硬件层面的协同设计,利用SFQ电路构建了解码器。考虑到表面代码解码所需的处理的局部性,以及SFQ电路的特性,研究团队研究了分布式处理方式的图形匹配算法,并设计了执行这种算法的解码器。设计的解码器不需要大规模存储器,采用由支持各个辅助量子比特的简单处理单元相互交换几比特信号的结构,能以低功耗运行,而且具有优异的可扩展性。

另外,研究团队还首次提出了可在现实环境中运行的同时观测和解码辅助量子比特的“在线处理式”解码方式及具体的安装。在超导量子计算机中,辅助量子比特的观测处理以约1微秒的间隔重复进行,而研究团队提出的解码器能在1微秒以内完成解码处理,具备在线处理所需的高速性。

迄今为止,可实际应用的大规模量子计算机的设计问题一直是构建量子计算机的最大课题。尤其是此次涉及的纠错解码器,在设计上需要实现能随着量子计算机的规模增大而变得复杂的算法进行高速处理,是整个量子计算机中最难设计的部分之一。

原文:《科学新闻》

翻译编辑:JST客观日本编辑部